Issue 7/2006 www.edn.com

Economies of Freescale Pg 30

Happy birthday to us Pg 10

Milestones that mattered: RAMAC and random memory <u>Pg 36</u>

Scaling: a balanced view, part one Pg 40

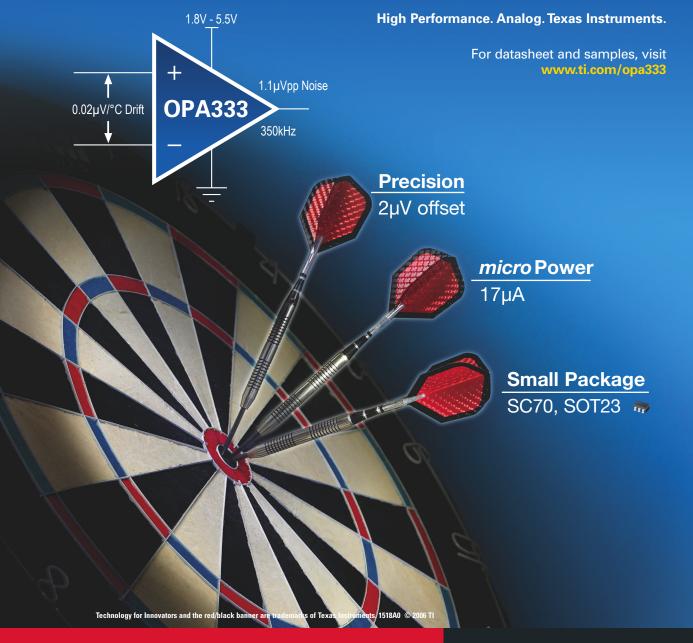

# Right on Target

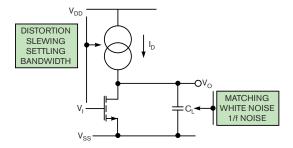

# Zerø-Drift Operational Amplifier

The new OPA333 zero-drift operational amplifier combines excellent precision, micropower and tiny packaging to achieve breakthrough performance. Featuring operation down to 1.8V, the OPA333 targets demanding applications in medical instrumentation, temperature measurement, test equipment and consumer systems.

# WORLDWIDE SELECTION PERSONALIZED SERVICE

Access to over **540,000** part numbers from more than **320** quality, name-brand manufacturers!

#1 for Breadth of Product

**#1 for Availability of Product**

**#1 for On-Time Delivery**

**#1 for Overall Performance**

Source: EE Times Distributor Evaluation Study, September 2005

CORPORATION

1.800.344.4539

AME-DAY HIPMENT

www.digikey.com

Don't let poor performance spoil your designs. With high performance AVR® microcontrollers you can create applications with no worries about the microcontrollers performance. AVR Flash microcontrollers operate with clock rates up to 20 MHz, achieving close to 20 MIPS. With 32 general purpose registers, the AVR delivers unmatched performance and flexibility while reducing power consumption to a minimum.

Learn more and try to unmask the Super AVR at www.atmel.com/ad/superAVR

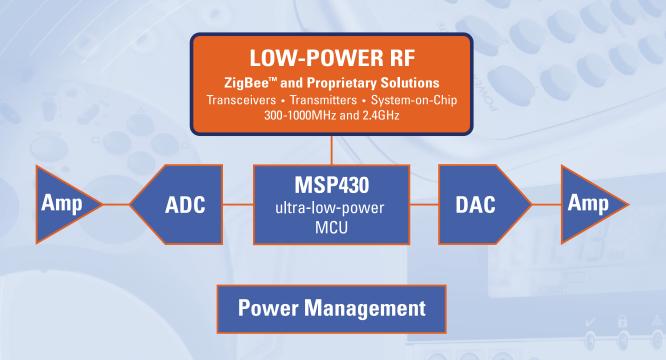

# TI + CHIPCON

# **COMPLETE LOW-POWER RF SOLUTIONS**

#### **CONSUMER APPLICATIONS**

- Wireless keyboard/mouse

- Wireless gaming accessories

- Wireless VolP solutions

- Remote controls

#### **BUILDING AUTOMATION APPLICATIONS**

- Building control and monitoring

- Tracking systems

- Automatic meter readers

- Alarm and security systems

Order the new Low-Power RF Selection

Guide and subscribe to the low-power RF

e-Newsletter at <a href="https://www.ti.com/low-powerRF">www.ti.com/low-powerRF</a>

With the acquisition of Chipcon, TI now provides you with industry leading ZigBee<sup>™</sup>-compliant solutions and a broad range of proprietary RF-ICs that enable innovative low-power wireless applications. And, Chipcon's software, development kits and reference designs will speed your time to market.

TI's portfolio of high-performance analog and ultra-low-power MCUs combined with Chipcon's low-power RF-ICs give you an immediate low-power RF offering and a strong roadmap for future integrated solutions.

Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1519A0 © 2006 TI

# REDUCE DEVELOPMENT COST!

# TALK TO US

800-496-5570

**REDUCE** your power development cost by specifying Vicor modular DC-DC converters. We offer the widest range of standard input voltages, output voltages, and power levels in the industry. They all come with complete safety agency approvals, and Vicor's high power densities allow more flexible packaging. A full range of online design tools and access to our worldwide applications engineering staff help ensure that you achieve the most cost-effective power design.

**TALK TO US**, and receive your <u>FREE Multimeter</u>. You'll find out how you can reap the benefits of designing with Vicor high-density DC-DC converters. Faster time to market, greater power density and performance, and higher reliability are always affordable. Call 800-496-5570 or go to vicorpower.com/edn for more information.

Always Affordable!

vicorpower wood

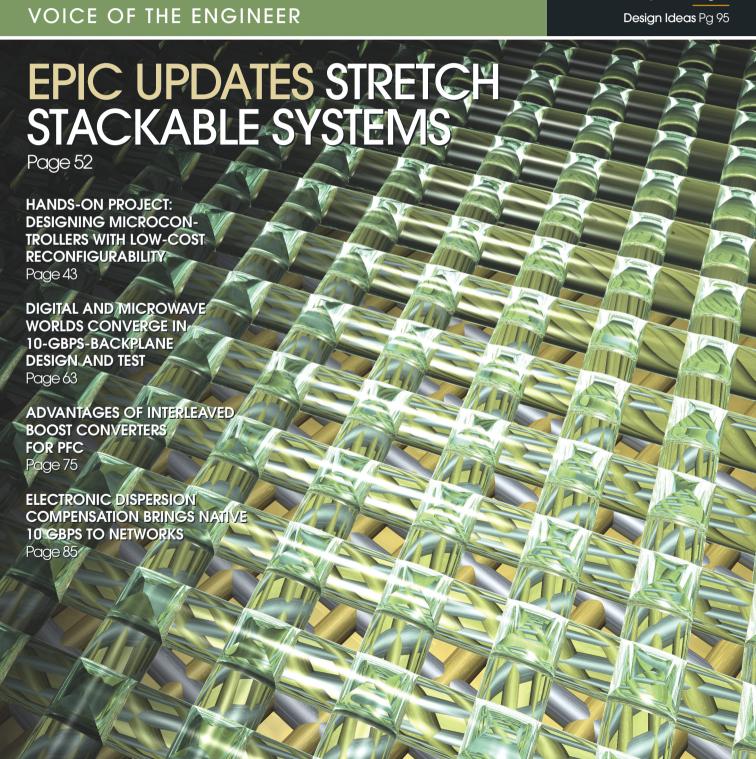

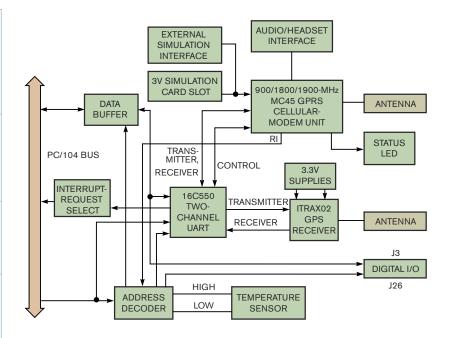

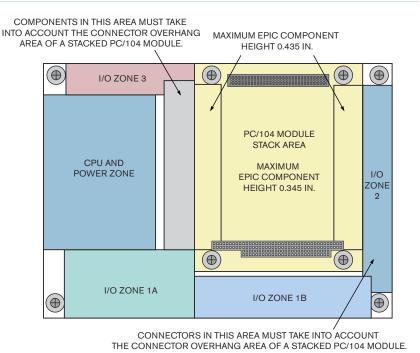

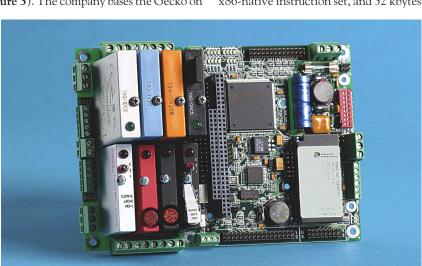

#### **EPIC** updates stretch stackable systems

Two new board-level standards offer PC/104 designers more real estate, a link to fabric technology, and continued compatibility with legacy hardware. by Warren Webb, Technical Editor

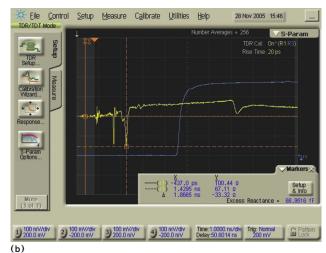

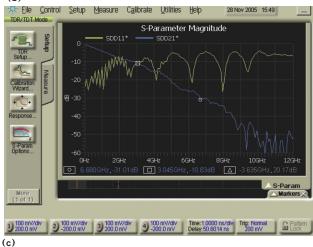

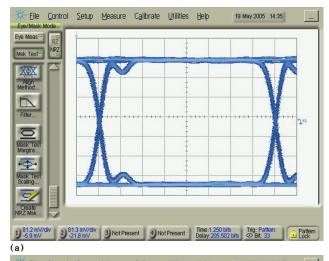

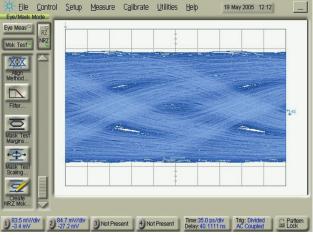

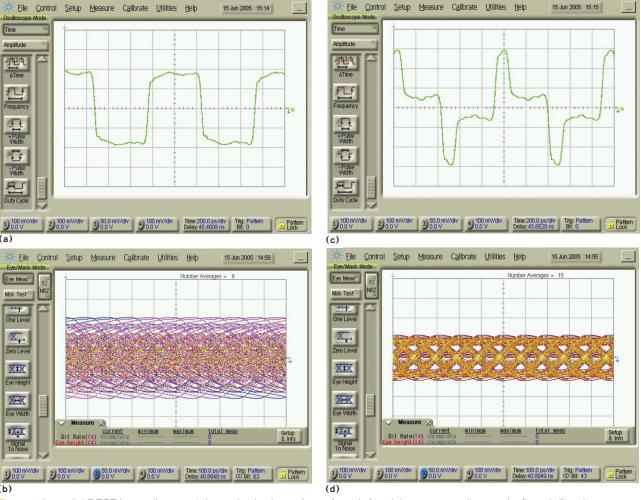

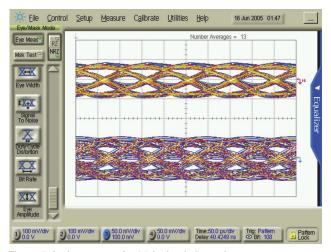

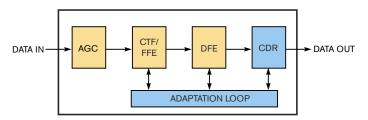

#### Digital and microwave worlds converge in 10-Gbps-backplane design and test

Getting usable signals through backplanes is far from trivial when speeds reach 10 Gbps. By predistorting and equalizing signals, driver and receiver ICs allow the use of low-cost substrate materials, but good designs are no accident.

> by Shannon Sawyer, Intel Corp and Greg Le Cheminant, Agilent Technologies

### Hands-on project: designing microcontrollers with low-cost reconfigurability

Reconfigurable microcontrollers offer an impressive array of analog and digital features to meet your application's requirements.

by Nicholas Cravotta, Contributing Technical Editor

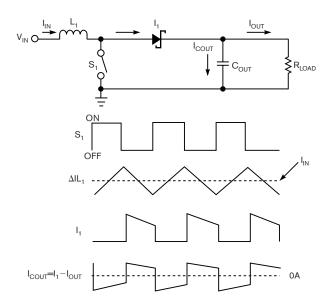

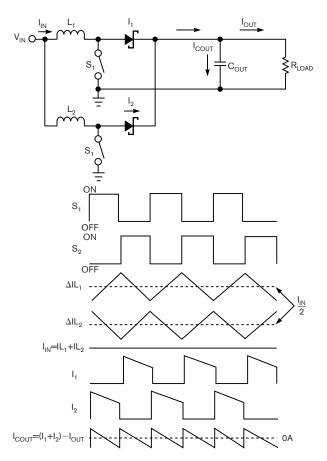

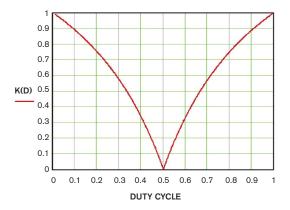

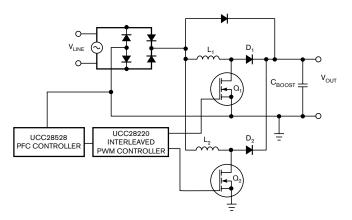

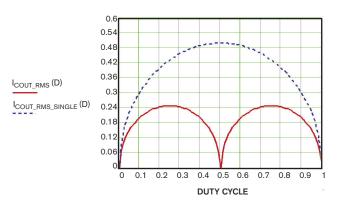

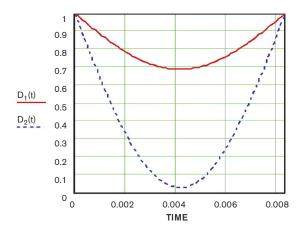

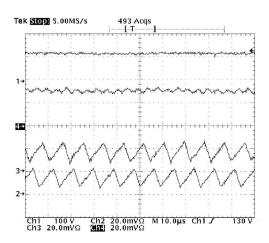

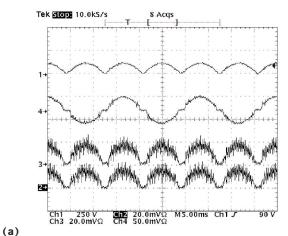

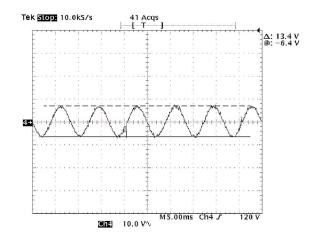

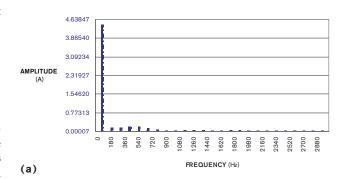

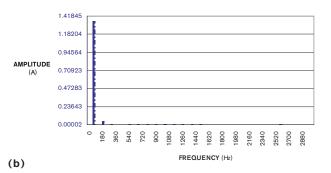

#### Advantages of interleaved boost converters for PFC

Interleaving boost stages can reduce power-factor-corrected-preregulator power-converter input- and output-ripple currents that in turn reduce the boost-inductor size and the output capacitor's electrical stress.

by Michael O'Loughlin, Texas Instruments

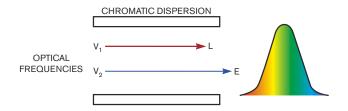

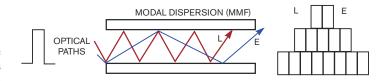

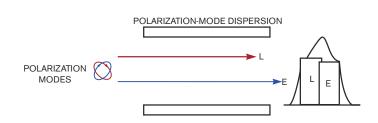

#### **Electronic dispersion** compensation brings native 10 Gbps to networks

At 10 Gbps, dispersion has a dominant effect on optical-link performance for long- and short-haulnetworking applications. To handle this dispersion, developers must either upgrade the fiber infrastructure or implement dispersion compensation.

> by Michael Furlong and Ali Ghiasi, Broadcom Corp

# DESIGNIDEAS

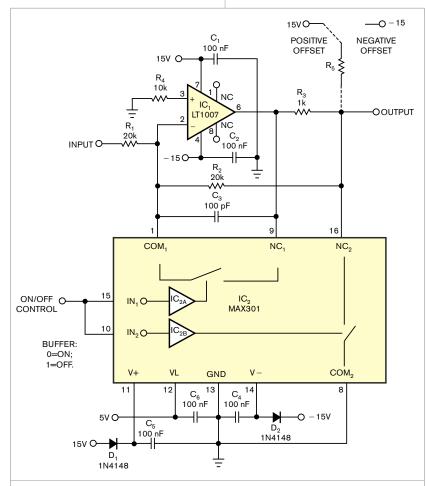

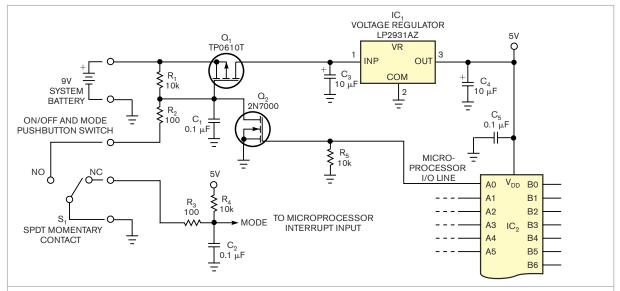

- 95 On/off buffer switches analog or digital signals

- 96 Single switch serves dual duty in small, microprocessor-based system

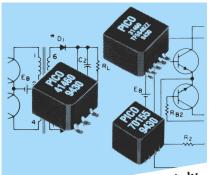

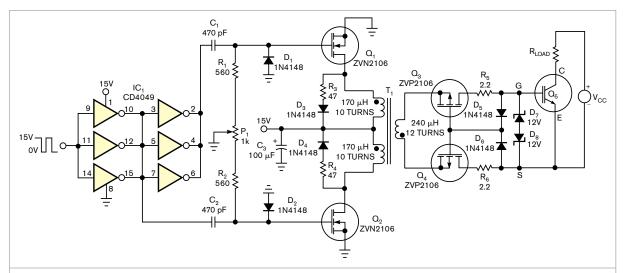

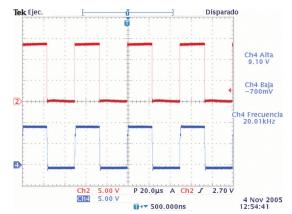

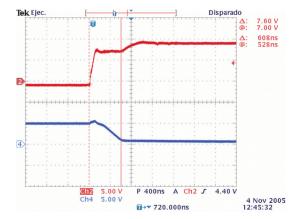

- 98 Isolated-FET pulse driver reduces size, power consumption

- Send your Design Ideas to EDNdesignideas@reedbusiness.com.

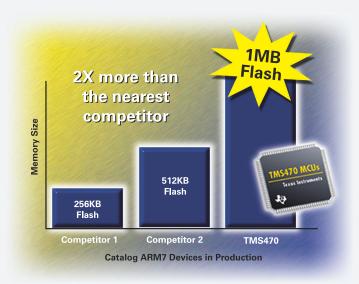

# 1MB Flash ARM7<sup>™</sup> MCU

#### ▶ Features

- 1MB integrated Flash

- ARM7TDMI® based MCU

- RISC co-processor

- Expansion bus module

- High-end CAN controller

- 10-bit buffered ADC with 1.55µs conversion

- Memory security module

- Up to 60MHz performance

#### We Know ARM.

TMS470 ARM7TDMI® core-based microcontrollers, with **industry-leading 1MB Flash**, are now in production and available to the general purpose market. The TMS470R1B1M expands on the TMS470 portfolio featuring **7 versatile devices with more than 256KB of Flash**. These are combined with advanced peripherals to provide maximum design flexibility and system performance.

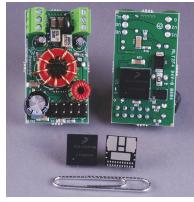

The **TMS470 System KickStart Kit** (TMDS-FET470R1B1M) includes the hardware and software needed to start development today. The Kit evaluation board can also be used as a drop-in module in Tl's High-Performance Analog Evaluation Kit (HPA-MCUINTERFACE) to form the industry's first modular complete signal chain development kit.

Register for TMS470 Seminar and 1/2 Price System Kickstart Kit – Only \$199

www.ti.com/arm7 o 800.477.8924, ext. 3163

### contents 3,30,06

- 25 Power-management IC suits advanced microprocessors' power needs

- 25 Novas introduces on-the-fly debugging

- 26 Tools take asynchronous design mainstream

- 28 1U, half-rack switching units' debut kicks off supplier's LXI push

- 28 Chip improves efficiency of flyback-converter circuits

- 30 Voices: Economies of Freescale with Michel Mayer

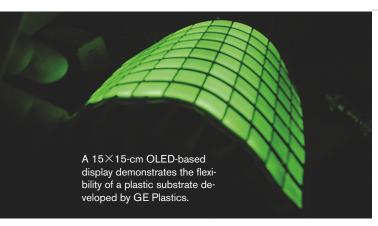

- 32 Research Update: Plastic substrate allows OLED displays to get bent; Standard silicon conjures continuous laser; Nanotube-based ultracapacitors could rival batteries

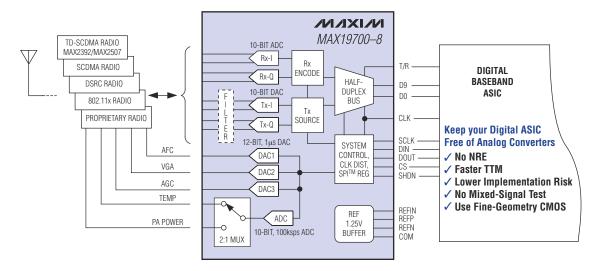

- 34 Global Designer: DAQ chips simplify sensor interfaces; Headphone amp swaps modes to cut noise, save power

### DEPARTMENTS & COLUMNS

- 10 **EDN.comment:** Happy birthday to us

- 36 Milestones that mattered: RAMAC launched diskdrive revolution; Random memory

- 38 Signal Integrity: Terminator II

- 40 Analog Domain: Scaling: a balanced view, part one

- 110 Reality Check: Long-promised game may yet appear

# PRODUCT

- 104 Discrete Semiconductors: MOSFETs, high-current drivers, and more

- 105 Computers and Peripherals: Hard-drive family, storage processor, PCI Express broadcast decoder, and more

- 106 Embedded Systems: Carrier blade, wireless-family development kits, PCI CPU, and more

EDN ® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Slephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN @ copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year; Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 51, Number 7 (Printed in USA).

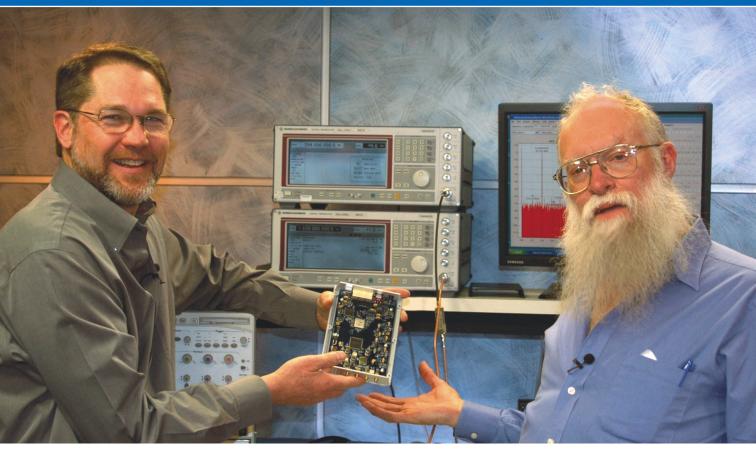

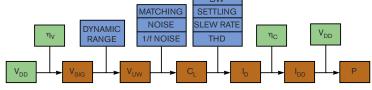

# Watch Bob Pease and Dr. Howard Johnson Get Real About High-Speed Data Transfer

#### Tune In Today to National Semiconductor's Analog by Design Show!

Covering analog, digital and everything in between, including:

- Trade-offs of noise, speed, and resolution in high-speed data transfer

- Two ways to receive data from GHz speed A/D converters

- Distinguishing A/D converter performance from the quality of its signal source

Part 1 is available now. Part 2 available March 28, 2006 www.national.com/analogbydesign

# ED online contents

#### ONLINE ONLY

Check out these online-exclusive articles.

#### The square root of the sum of the squares

If you have to generate an analog voltage proportional to the module of a vector whose components are also available in analog form, you can adopt a classic solution involving the use of analog multipliers.

www.edn.com/article/CA6312102

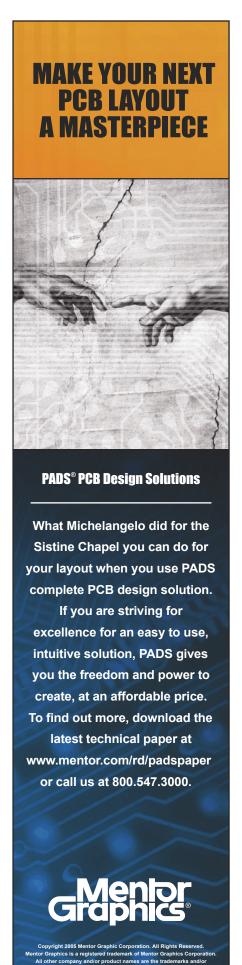

#### DFM tool helps with "lithographyfriendly" layouts

Mentor Graphics claims that its latest DFM (design-for-manufacturing) offering will help IC designers make "lithographyfriendly" IC layouts.

www.edn.com/article/CA6313706

#### Microcontroller vendors further encroach on SOCs

Vendors of high-end microcontrollers are smelling opportunity that in the past might have gone automatically to OEM-designed SOCs (systems on chips).

www.edn.com/article/CA6312649

#### Connectivity activity: Wireless USB, Bluetooth, DLNA

When it comes to digital-consumer gadgets, the term "stand alone" simply does not compute. It's all about connectivity.

www.edn.com/article/CA6316098

#### Serial links take on roles in clamshelldesign connections

Designers struggle with reliable ways to connect a screen to the main electronics subsystem, especially in phones and cameras in which the upper half of the shell can rotate.

www.edn.com/article/CA6312719

#### INNOVATION AWARD WINNERS

EDN will announce the winners of the 16th **Annual Innovation** Awards April 3 at a special event in San Jose, CA. Tune in on April 4 to find out who won.

→ www.edn.com/ innovation

#### FROM THE VAULT

Articles and extras from the EDN archives that relate to this issue's contents.

#### TERMINATOR II (pg 38):

#### Terminator

Part one of Howard Johnson's series appeared in the March 3 issue.

→ www.edn.com/article/CA6309116

#### SCALING: A BALANCED VIEW (pg 40):

→ www.edn.com/article/CA191157

### Ripples in the process pool

#### EPIC UPDATES STRETCH STACKABLE SYSTEMS (pg 52):

#### Quad DSP engine features switchedfabric data streams

#### → www.edn.com/article/CA6305359

#### EPIC computer pushes temperature extremes

→ www.edn.com/article/CA6258648

#### PC/104 Consortium to take over EPIC

www.edn.com/article/CA498707

#### DESIGNING MICROCONTROLLERS WITH LOW-COST RECONFIGURA-**BILITY** (pg 43):

#### One design fits all

→ www.edn.com/article/CA6255076

#### READER'S CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### Design Idea: Simple digital filter cleans up noisy data

Clean up data from pressure and temperature sensors.

www.edn.com/article/CA6309111

#### Design Idea: Low-cost audio filter suppresses noise and hum

Passive filter requires no dc power. www.edn.com/article/CA6309113

#### Stanley's Law: IC design follows pc-board design

An old friend made a brilliant observation: "Everything that happens in IC design, happened in pc-board design many years ago."

www.edn.com/article/CA6309115

#### Antenna tunes in to needs of satellite-radio designers

Sarantel's antenna has won a spot in the soonto-ship generation of portable satellite-radio receivers built for the

XM Satellite Radio service.

www.edn.com/article/CA6311792

#### Linux joins the consumer-electronics revolution

Designers are turning to the Linux operating system to meet the escalating user-interface, networking, and multimedia requirements of today's consumer-electronics products.

www.edn.com/article/CA6305349

#### BY MAURY WRIGHT. EDITOR IN CHIEF

## Happy birthday to us

t's a special birthday for EDN this year: our 50th. Some of you may have noticed the 50th-anniversary logo that we've included in EDN in recent issues. We've also begun running excerpts in the Pulse section from issues that span our past. We have quite a bit more in store for you as the year goes on. This issue, we launch "Milestones That Mattered," a page that will run monthly through the end of the year. We will choose milestones from our 50-year history that were important when they first occurred and that, even after five decades, still have an effect on key technologies.

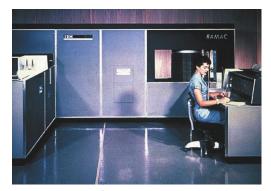

Our first milestone is the IBM 305 RAMAC computer (pg 36) that IBM launched in September 1956, just a few months after the May launch of EDN as a stand-alone publication. EDN then covered all types of electronic end products and enabling technologies with which

engineers could build products. A computer filled the bill in those days even though it was decidedly targeted at what we'd now call "information technology." But RAMAC, with its 350 Disk File, also laid the foundation for the disk drives of today that enable everything from MP3 players to per-

sonal video recorders to industrial-control systems—and computers.

The occasion of our golden anniversary also led us to look back at other special issues of EDN. In the 1970s, EDN was the first publication to provide in-depth coverage of microprocessors. In the 1980s, we provided

> landmark coverage of the birth of ASICs; we even had staff members design several ASICs. And in the 1990s, we were at the forefront of the Internet age, launching a Web site in 1995, and you can still access those archives today. Design Ideas, a department that remains incredibly popular with readers, has been a part of EDN since the very first issue.

> The 25th-anniversary issue has been a joy to review. Contributors—both EDN staffers and participants from the industry—proved

remarkably savvy in looking forward. We've run several excerpts as examples. The predictions included broadband networks to the home and the convergence of computers, communications, and consumer electronics. Here's an example:

"Where will we be in 25 years? The availability of inexpensive computing will have considerable impact. Many more functions will be performed by digital computers. Voice communication over expensive media (wire, mobile radio) will occur digitally to save bandwidth and improve privacy via encryption. Many control functions within our household appliances and

We will choose milestones from our 50-year history that were important when they first occurred and that, even after five decades, still have an effect on key technologies.

motor vehicles will be performed by digital computers because the more intelligent control they offer will utilize expensive resources more efficiently."—ME Hoff, Intel Corp, EDN, Oct 14, 1981.

We will share more of that 25thanniversary issue with you throughout the remainder of 2006. Meanwhile, please let me know of any milestones that you think should be on the list. If there is a technology visionary that you'd like to hear from, let me know.EDN

Call me at 1-858-748-6785 or e-mail me at mgwright@edn.com.

The IBM RAMAC (random-access-method-ofaccounting-and-control) computer was the first digital computer to use a disk drive and that allowed near-real-time manipulation of database records (courtesy Magnetic disk Heritage Center).

Thermal

Thermal Magnetic

Magnetic

High Performance

Electronic

# **3120-F7**Applications include: marine, medical and office equipment, appliances and tools.

# No two circuit breaker applications are alike

# Only E-T-A offers more technologies

Many circuit protection applications appear the same but every application is different requiring a specific circuit protection solution. Only E-T-A provides the most complete range of available circuit protection technologies.

More technologies allow for superior, more precise circuit protection. It is critical that your design is protected with the correct circuit protection. Your reputation depends on it.

One call to E-T-A will ensure your design has the right circuit protection technology to enhance your products safety, reliability and brand reputation.

Go to www.e-t-a.com/ipod1 for your chance to win one of 10 video iPods®

# Intelligent data acquisition with Ramtron MCUs

Maximize design flexibility and system performance Minimize cost and time to market

Ramtron microcontrollers are feature-rich data acquisition solutions ideally suited for your industrial, consumer, medical, computer, telecom and automotive applications.

Our Versa Mix 8051 MCUs are a family of high performance, 8-bit mixed-signal controllers with on-chip DSP capabilities and comprehensive peripheral support. As a

complete data acquisition SoC, the Versa Mix 8051 is ideal for a variety of signal conditioning, processing, control, and sensor applications.

We also offer a "single-chip solution" for embedded instrumentation and control applications with our Versa 8051 Family of MCUs, with up to 40-MIPS operation and rich peripheral support.

#### Versa Mix 8051 Microcontrollers

- Single-Cycle 8051 Processor

- Enhanced MULT/ACCU Unit & Barrel Shifter

- Enhanced SPI, I<sup>2</sup>C-Compatible Interface

- UARTs, RS-485/RS-422/J1708-Compatible RxTx

- 5/7-Channel A/D Converter

- Programmable Current Source

- Digital Potentiometers, Analog Switch, Op Amp

- PWM D/A Outputs

- Hardware and Software Development Tools

Download a free MCU selection guide at ramtron.com

Combine Ramtron microcontrollers with our high-performance nonvolatile FRAM memory to create truly unique data acquisition solutions.

To find out how Ramtron MCUs and FRAM memory can raise the standard in your next design, call **1-800-943-4625**. ext. **208**. or email

RAMIRUN International Corporation

www.ramtron.com

mcuinfo@ramtron.com.

#### PUBLISHING DIRECTOR, EDN WORLDWIDE

John Schirmer

1-408-345-4402; fax: 1-408-345-4400 jschirmer@reedbusiness.com

#### EDITOR IN CHIEF

Maury Wright 1-858-748-6785 mgwright@edn.com

#### EXECUTIVE EDITOR

Ron Wilson 1-408-345-4427 ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasey Clark Contact for contributed technical articles 1-781-734-8436; fax: 1-781-290-3436 kase@reedbusiness.com

#### EXECUTIVE EDITOR, ONLINE

Matthew Miller 1-781-734-8446; fax: 1-781-290-3446;

mdmiller@reedbusiness.com SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646 wwebb@edn.com

#### ANALOG/COMMUNICATIONS. DISCRETE SEMICONDUCTORS

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### EDA. MEMORY.

PROGRAMMABLE LOGIC Michael Santarini, Senior Editor;

1-408-345-4424 michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs. TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070 rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA,

PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

#### POWER SOURCES.

ONLINE INITIATIVES Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

#### DESIGN IDEAS EDITOR

**Brad Thompson**

#### edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-928-1403; mbutler@reedbusiness.com

#### **EDITORIAL AND ART PRODUCTION**

Diane Malone, Manager; 1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production Editor 1-781-734-8442: fax: 1-781-290-3442 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net

#### COLUMNISTS

Howard Johnson, PhD Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu. Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.ip Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.ip

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community

#### **DENNIS BROPHY**

Director of Business Development Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV System Architect, Intel

#### RON MANCINI

Staff Scientist, Texas Instruments

#### GABRIEL PATULEA

Design Engineer, Cisco

#### MIHIR RAVEL

VP Technology, National Instruments DAVE ROBERTSON

#### Product Line Director, Analog Devices

SCOTT SMYERS

VP Network and System Architecture Division, Sonv

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000;

fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### No two circuit breaker applications are alike

#### Only E-T-A offers more technologies

#### ESS20-1

Prevent an overload on one circuit from shutting down the entire production line. Designed for switch-mode power supplies. www.e-t-a.com/ess2oedn

#### E-1048-800

Remote power controller utilizes "SMART" circuit protection technology. Circuit breaker, relay, analog output, and diagnostics in a single unit

www.e-t-a.com/e1048edn

WWW.E-T-A.COM 1-800-462-9979

### **Microsoft**

# Apples and Oranges Working Together... That's the Power of Windows Embedded

The developers at Fujitsu know that the hundreds of peripheral drivers included in the Windows® CE operating system provide the solutions they need to easily integrate multiple device functions.

Needing to incorporate drivers for an infrared receiver, 802.11g WiFi card, and touch screen, the Fujitsu U-Scan Shopper development team chose Windows CE. Because Windows CE offers familiar, yet easily customized components and tools, they were able to develop the device in only five months. With the power of Windows CE, the Fujitsu U-Scan Shopper offers users coupons on demand, infrared scanners for product promotions, and in-store order placement, all from the convenience of the produce section, or wherever your shopping cart takes you.

We considered Linux, but couldn't have achieved the same results, so we chose the Windows CE operating system."

— VERNON SLACK / Store Solutions / Fujitsu Transaction Solutions

The Power to Build Great Devices—get it with Windows CE, Windows XP Embedded, or Windows Embedded for Point of Service.

www.learnaboutembedded.com/shopping --->

# **Performance Beyond Limits**

... ready for Extreme Embedded Computing?

INSERT-READY

ACCELERATED DESIGN

SCALABILITY

LONGEVITY

COST-EFFECTIVE

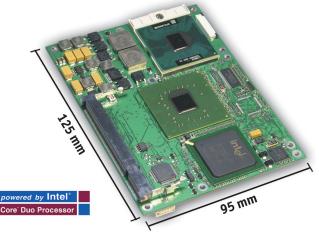

#### ETXexpress-CD

- ➤ Highest performance state-of-the-art embedded module

- ➤ Intel® Core® Duo processor and Intel® 945GM chipset

ETXexpress products are next generation embedded modules based on the PICMG COM Express standard. ETXexpress provides the hightest performance and I/O bandwidth available in COMs.

- > PCI Express the elemental data path

- Gigabit Ethernet for high connectivity

- ➤ USB 2.0 for fast periphery

- > Serial ATA for fast drives

- ACPI for optimized power management

**Get ready. Get ETXexpress**Visit www.kontron.com/ETXexpress

Intel®

Communications

Alliance

Premier Member

Computer-On-Modules

Blades & Mezzanines

CPU Boards

Systems

Mobile Rugged

Custom Solutions

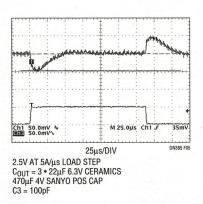

# POWER designer

Expert tips, tricks, and techniques for powerful designs

No. 111

| Feature Article1-                | 7 |

|----------------------------------|---|

| 2.5A Buck Switching<br>Regulator | 2 |

| 0.5A Buck Switching<br>Regulator | 4 |

| 1A Buck Switching<br>Regulator   | 6 |

| Power Design Tools               | 8 |

|                                  |   |

|                                  | 1 |

# Buck Regulator Topologies for Wide Input/Output Voltage Differentials

— By Bob Bell, Applications Engineer and David Pace, Design Manager

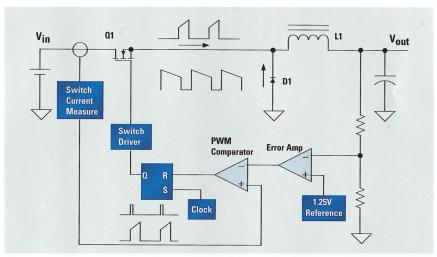

Figure 1. Buck Regulator Using Current-Mode Control

uck regulators are used to efficiently step down a higher level, unregulated input voltage to a regulated output voltage. In applications requiring DC-DC conversion from a high input voltage, the buck regulator dramatically improves conversion efficiency relative to linear regulator alternatives. However, applying the buck regulator to applications with high input-to-output step-down ratios creates significant challenges for the pulse-width modulation (PWM) controller. Because the duty cycle of the buck regulator switch is approximately equal to V<sub>OUT</sub>/V<sub>IN</sub>, a buck DC-DC converter with high input/output voltage ratio must control very narrow PWM pulses. The switching frequency of a buck regulator is generally set to a high level to reduce the size of the inductor and capacitors. High switching frequency and low duty cycle translates to very short pulse durations in the controller. For example, a buck regulator with an input voltage of 66V and an output voltage of 3.3V will require a buck switch duty cycle of approximately 5%. At a typical switching frequency of 300 kHz, the required PWM on-time of the buck switch is a mere 166 ns.

Control methods or topologies used in buck regulators include Voltage-

#### **NEXT ISSUE:**

**Trade-offs in Synchronous Design**

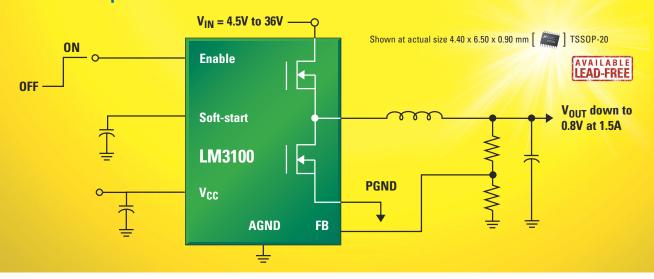

### **Integrated 42V, 2.5A Buck Switching Regulator**

# National's LM25005 With Emulated Current-Mode Control Reduces Noise Sensitivity and Enables Reliable Control of Small Duty Cycles at High Input Voltages

#### LM25005 Features

- Ultra-wide V<sub>IN</sub> from 7V to 42V, supports load currents up to 2.5A

- Adjustable output voltage from 1.225V

- 1.5% feedback reference accuracy

- Current mode control with emulated inductor current ramp

- Programmable switching frequency with bi-directional synchronization capability simplifies system design

- · Simulation support available

- Available in TSSOP-20EP (Exposed Pad) packaging (AVAILABLE)

Ideal for use in consumer electronics, telecommunications, data communications systems, automotive power systems, and distributed power applications

#### **Product Highlight:**

Allows multiple devices to self-synchronize or synchronize to an external clock

# POWER | designer

#### **Buck Regulator Topologies for Wide Input/Output Voltage Differentials**

Mode (VM), Current-Mode (CM), Hysteretic, and Constant-On-Time (COT) control. Current-mode control provides ease of loop compensation, FET switch protection, and inherent line feed-forward compensation. This makes current-mode control a favorite among power designers.

Hysteretic and Constant-on-Time controllers respond more quickly to load transients but do not operate at constant switching frequency. Constant-on-Time, a variant of hysteretic control, provides improved stability and less variation in switching frequency.

#### **Current-Mode Control**

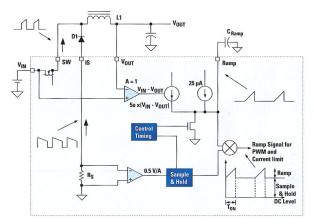

Buck regulator ICs intended for high input/output step-down ratios must provide robust noise immunity when operating with very narrow duty cycles. In a current-mode topology, the challenge is the measurement and scaling of the inductor current. *Figure 1* shows the block diagram of a current-mode buck regulator. The output voltage is monitored and compared to a reference, with the error signal applied to the PWM comparator. The modulating ramp is a signal proportional to the buck switch current. When the buck switch is turned on, the inductor current flows through it with a slope of (V<sub>IN</sub> – V<sub>OUT</sub>) / L. An accurate, fast measurement of the buck-switch current is necessary to create the PWM ramp signal.

Propagation delays and switching transients makes it difficult to use current-mode control for large conversion ratio applications where very small on-times are required. Even with the best design practices, current sense and level shift circuits will add significant propagation delay. In addition, when the buck switch turns on, the reverse recovery current into the free-wheeling diode (D1) causes a leading-edge current spike with an extended ringing period (See *Figure 2*.) This spike can cause the PWM comparator to trip prematurely. Attempts to filter or blank this leading-edge spike reduces the minimum controllable on-time of the buck switch.

#### **Emulated Current-Mode Control**

The challenge of accurate and fast current measurement can be met with a new proprietary method that emulates the buck switch current without actually measuring the current. The buck-switch current waveform can be broken down into two parts—a base, or pedestal, and a ramp. The pedestal represents the minimum (or valley) inductor current level. The inductor current falls to its minimum just before the buck switch turns on. A sample-and-hold measurement of the free-wheeling diode current, taken just prior to the turn-on of the buck switch, can capture the pedestal current information.

The other part of the buck-switch current waveform is the positive ramp to the peak level. The ramping current slope is described by,  $\textit{dildt} = (V_{IN}\text{-}V_{OUT}) \ / \ L$ . A signal equivalent to the current ramp can be created with a current source proportional to  $V_{IN}\text{-}V_{OUT}$  and a capacitor  $(C_{RAMP})$ . If the current source  $(I_{RAMP})$  is controlled by the difference between the input and output voltages, the capacitor charging slope is:  $\textit{dvldt} = K^* \ (V_{IN} - V_{OUT}) \ / \ C_{RAMP}$ , where K is a constant scale factor for the current source. The value of  $C_{RAMP}$  can be selected to set the capacitor voltage slope proportional to the inductor current slope.

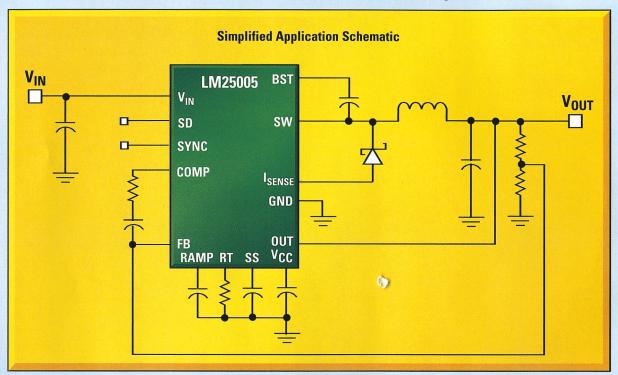

Figure 2. Emulated Current-Mode Regulator

Figure 2 presents the block diagram of the LM25005, an integrated buck regulator that implements the emulated current-mode control scheme described above. The free-wheeling diode anode is connected to ground through the

## Highly Integrated 42V, 0.5A Buck Switching Regulator

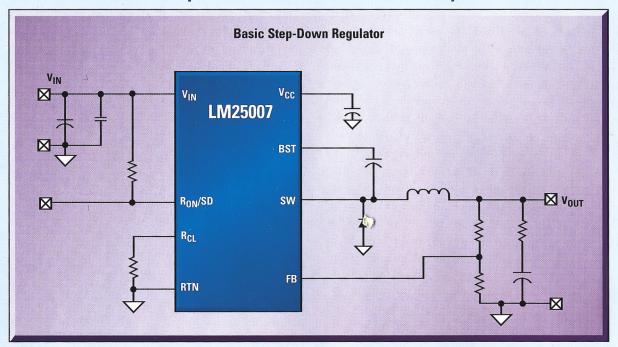

# LM25007 Has Constant-On-Time Architecture with V<sub>IN</sub> Feed-Forward, Provides Ultra-Fast Transient Response, and Needs No External Components

#### LM25007 Features

- Wide V<sub>IN</sub> from 9V to 42V, supports load currents up to 0.5A

- Ultra-fast transient response, reduced filter capacitance

- Up to 800 kHz switching frequency

- · Precise DC current limit

- ±2% accurate, 2.5V feedback from -40° to 125°C

- · Integrated high voltage bias regulator

- Available in thermally enhanced MSOP-8 and LLP packaging

Ideal for use in automotive electronics, telematics, Industrial systems, consumer electronics, distributed power supplies, high-voltage post regulators, industrial power supplies, and high-efficiency point-of-load (POL) regulators

#### **Product Highlight:**

$V_{\text{IN}}$  feed-forward provides near constant operating frequency

For FREE samples, datasheets, and more information, visit www.national.com/pf/LM/LM25007.html

# POWER designer

#### **Buck Regulator Topologies for Wide Input/Output Voltage Differentials**

controller. A small-value, current-sense resistor and amplifier are used to measure the diode current. A sample-and-hold circuit captures the minimum level diode current just prior to the turn-on of the buck switch. Sampling the valley current, each cycle provides the pedestal portion of the emulated current sense signal.

The LM25005 senses the input voltage and the output voltage to generate a current source that charges an external ramp capacitor (C<sub>RAMP</sub>). When the buck switch is turned on, the capacitor voltage rises linearly during each cycle. When the buck switch is turned off, the capacitor is discharged. For proper operation, the ramp capacitor is chosen in proportion to the value of the buck inductor. The LM25005 sums the sampled current pedestal and the external ramp capacitor voltage and applies this signal to the PWM comparator. The final result is a controller that behaves like a peak current-mode controller but without the delay and transient effects in the current sensing signal.

For applications operating with duty cycles greater than 50 percent, peak current-mode controllers are subject to sub-harmonic oscillation. Oscillation is normally avoided by adding an additional fixed slope ramp to the current-sense signal (slope compensation). In the LM25005, an additional fixed offset current provides an additional fixed slope to the ramp capacitor signal. For very high duty cycle applications, the ramp capacitor value can be decreased to further increase the ramp slope and prevent sub-harmonic oscillation.

LM25005 output overload protection is accomplished with a dedicated current-limit comparator which limits the emulated peak current on a cycle-by-cycle basis. The emulated current-mode method

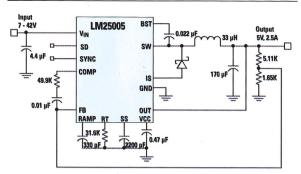

Figure 3. LM25005 Buck Regulator Schematic

provides the added benefit of capturing inductor current information prior to the buck switch turnon. If the current pedestal exceeds the current-limit comparator threshold due to an extreme overload condition, the buck switch skips cycles to prevent current runaway.

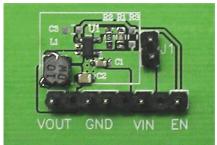

Figure 3 shows an LM25005 controlled buck regulator designed for an input voltage range of 7V to 42V and an output voltage of 5V with a maximum load of 2.5A.

#### **Constant-On-Time Control**

Another solution involving high input/output ratio buck regulators is Constant-On-Time control. This method can be thought of as a gated one-shot, where a feedback comparator triggers the next buck switch on-time when the output voltage falls below a threshold level. COT control is well suited for applications with high input/output voltage ratios because the one-shot can be programmed for a very short on-time and the feedback comparator will adjust the off-time to achieve the necessary low duty cycle. The noise sensitivity of a PWM ramp operating at low levels are completely eliminated. The COT technique has been used for many years for simple, cost-effective DC-DC converters because it requires no error amplifier or loop compensation components. The central issue of this method is frequency variation with input voltage and the possibility of sub-harmonic oscillation.

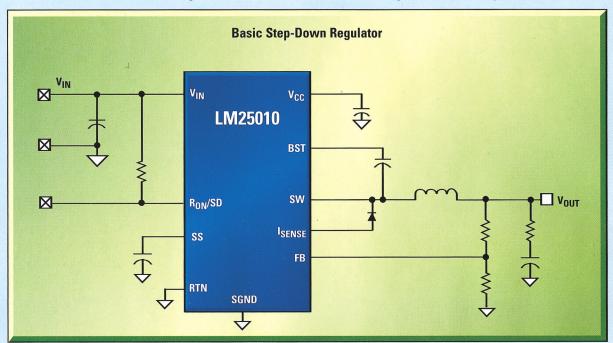

The block diagram in *Figure 4* illustrates the LM25010, a new member of a generation of COT buck regulators that solves these problems. The one-shot which controls the on-time is programmed by resistor R<sub>ON</sub> which is connected between the unregulated input voltage and the controller. The period of the one-shot (T<sub>ON</sub>) thus varies inversely with the input voltage. Using the simplified equation for the duty cycle (D) of a buck regulator, with Fs representing switching frequency:

$$\begin{array}{ll} D = \ V_{OUT}/V_{IN} \\ But by definition, & D = \ T_{ON}/(T_{ON} + T_{OFF}) = \ T_{ON} *Fs \\ Since, & T_{ON} = \ K/V_{IN} \\ Therefore, & Fs = \ V_{OUT}/K \end{array}$$

### Highly Integrated 42V, 1.0A Buck Switching Regulator

# LM25010 With Constant-On-Time Architecture and V<sub>IN</sub> Feed-Forward Provides Ultra-Fast Transient Response and Near-Constant Operating Frequency

#### LM25010 Features

- Wide V<sub>IN</sub> from 6V to 42V, supports load currents up to 1.0A

- Ultra-fast feed-forward response, modulated filter capacitance

- Switching frequency up to 1 MHz

- Valley current limiting at 1.25A

- ±2% accurate, 2.5V feedback from -40°C to 125°C

- Integrated high voltage bias regulator

- Available in exposed pad LLP-10 and TSSOP-14 packaging

Ideal for use in non-isolated telecommunications, secondary-side post regulators, and automotive electronics

#### **Product Highlight**

No control-loop compensation required

For FREE samples, datasheets, and more information, visit www.national.com/pf/LM/LM25010.html

# POWER designer

#### **Buck Regulator Topologies for Wide Input/Output Voltage Differentials**

Thus in any application where the desired  $V_{OUT}$  is a fixed value, the on-time can be programmed to achieve a desired switching frequency and the frequency will not vary significantly with changes in the input voltage.

One challenge associated with COT regulators is current limiting. If the on-time is terminated by a current-limit circuit which senses the current in the buck switch, the output voltage will fall and the off-time will decrease to its minimum value in an attempt to maintain voltage regulation. The frequency of the regulator will increase to an extremely high value, limited only by the propagation delays, and power dissipation within the IC will become excessive. Some buck regulator solutions arbitrarily enforce a minimum off-time after current limit is detected to guarantee that the frequency does not increase excessively in overload conditions. This approach produces a fold-back in the current limit I vs V characteristic which can limit the useful load range of the regulator.

The LM25010 illustrated in *Figure 4* solves the current limit dilemma with a simple yet effective method. The free-wheeling diode current is routed through a sense resistor in the IC. The current in the diode is sensed by a resistor and monitored by a comparator. If the current flowing through the free-wheeling diode exceeds the current-limit threshold, the current-limit comparator will disable the buck switch until the diode current falls to an acceptable level. The off-time is automatically increased to the

THERMAL STATEUP REGULATOR VCC UVLO ON/OFF THERMAL SHUTDOWN DRIVER LOGIC OVER-VOLTAGE OF THE STATEUP THERMAL SHUTDOWN SGND OVER-VOLTAGE OF THE STATEUP THERMAL SHUTDOWN SGND OVER-VOLTAGE OV

Figure 4. LM25010 COT Buck Regulator

time required for the buck inductor current to ramp down to the desired valley current. Thus, neither the output current nor the switching frequency can run away during overload.

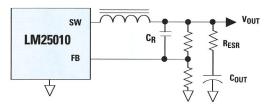

Regulators based on COT control are subject to erratic switching behavior if there is not sufficient ripple voltage present at the Feedback (FB) pin. If the output capacitor has a large enough Equivalent Series Resistance (ESR) this issue can be avoided. In applications where a relatively large output ripple cannot be tolerated, several ripple reduction techniques are available.

Figure 5a. COT Ripple Reduction Using C<sub>R</sub>

In *Figure 5a*, the ripple at  $V_{OUT}$  is fed to FB through  $C_R$ . Therefore the ripple at  $V_{OUT}$  can be less than in the standard circuit since it is not attenuated as much by the feedback resistors.

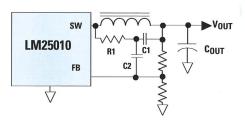

Figure 5b. COT Ripple Reduction Using R<sub>1</sub>,C<sub>1</sub>, and C<sub>2</sub>

In *Figure 5b*, the  $R_{ESR}$  is removed resulting in low ripple at  $V_{OUT}$ . The ripple required at FB is produced by  $R_1$ ,  $C_1$ , and  $C_2$ . Since  $V_{OUT}$  is an AC ground, and the SW pin switches between  $V_{IN}$  and ground, a sawtooth is generated at the  $R_1$ ,  $C_1$  junction.  $C_2$  then couples that ripple to FB.

These are some of the control methods and topologies favored by power designers. For more information on high-voltage switching power supply topologies, visit www.national.com/onlineseminars.

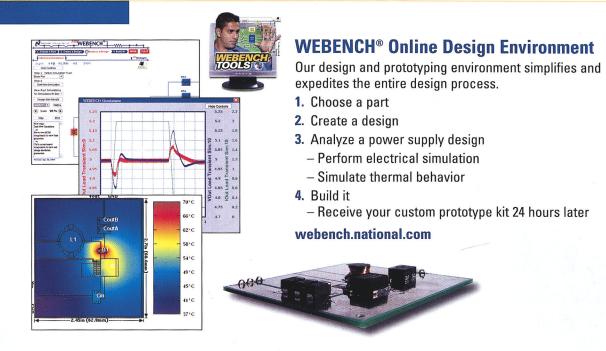

### **Power Design Tools**

### **Analog University®**

Expand your knowledge and understanding of analog with our free online educational training tool.

analogU.national.com

#### **National Semiconductor**

2900 Semiconductor Drive PO Box 58090 Santa Clara, CA 95052 1 800 272 9959

Visit our website at: power.national.com

For more information, send email to: new.feedback@nsc.com

Subscribe now to receive email alerts when new issues of Power Designer are available:

power.national.com/designer

Read our Signal Path Designer™ online today at:

signalpath.national.com/designer

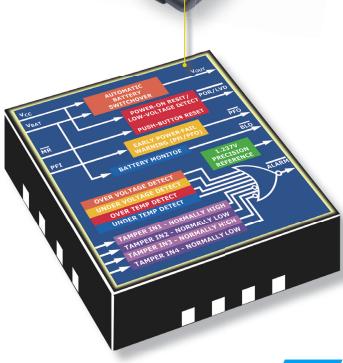

### Power-management IC suits advanced microprocessors' power needs

Ithough Freescale tailored the MC34703 Quiccsupply 3, the newest member of the Quiccsupply power-management family, to fit into the PowerQuicc III line of telecom and networking processors, it's equally wellsuited to other vendors' processors, according to Freescale Systems and Application Engineer Lonne Mays. "Many of today's advanced processors have both a core supply and an I/O supply that have requirements for how they track each other as they power up or down," he says. "With Quiccsupply, you can set the appropriate sequence for that processor." The device has a synchronous buck regulator for core voltages, providing current as high as 10A and a low-dropout controller

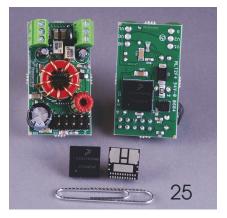

The Quiccsupply 3 power-management-IC evaluation board (top) follows the trend of combining several circuits onto one MCM (middle). The device provides currents as high as 10 and 2A.

for power I/O and bus voltages for current as high as 2A.

The device follows the trend of other recently introduced power controllers of combining several circuits onto one MCM (multichip module) but stops short of packing all external components into the device. "We keep the magnetics and other components external to gain flexibility," says Mays. "For example, if you need 5 rather than 10A, you could substantially shrink the magnetics and power supply."

The device switches nominally at 300 kHz but is adjustable from 200 to 400 kHz. Input voltages are 2.8 to 13.5V. The unit is available in a 10×10-mm, 33-lead PQFN package and sells for \$3.75 (10,000). An evaluation board costs \$100.30.-by Margery Conner

▶Freescale Semiconductor.

www.freescale.com

### Novas introduces on-the-fly debugging

Novas Software officials hope that the company's new product for on-the-fly debugging of IC code will prove to be as big a hit in the market as its Debussy and Verdi products are. Novas President and Chief Executive Officer Scott Sandler says that the new offering, Siloti, allows Novas debugging tools to dump signals on the fly during simulation and emulation without stopping the simulation or emulation. In today's SOC (system-on-chip)-verification environments, it is inconvenient and time-consuming to start and stop simulations and emulations to get signal dumps to

Siloti addresses this issue by taking what amounts to essential registers from the code on the fly to help the Debussy and Verdi tools get full visibility into signal behavior without halting simulation runs. Novas offers Siloti SimVE for simulation environments and Siloti SilVE for emulation, prototyping, and silicon debugging. The company claims that, for early customers of Siloti,

the product provides a fourfold decrease in debugging with hardware emulation and improves design visibility fivefold when users deploy it with a design-for-debugging methodology, in which RTL designers identify critical signals before performing simulations. Before designers simulate a design, they feed RTL or gate-level source code to Siloti. The tool then analyzes the code to determine which registers need to provide full visibility.

In an emulation environment, the SilVE tool performs sampling and analysis, signal expansion, and subsequent debugging of the design code rather than performing them on the netlist of the FPGA. Sandler says Siloti expands only the sections that users want to examine, which means that the simulator or emulator needs to dump just those parts of a file a user wants to examine. The Siloti SilVE and SimVE each start at \$65,000 for a one-year subscription.-by Michael Santarini

Novas Software Inc, www.novas.com.

### Tools take asynchronous design mainstream

DA and IP (intellectualproperty) start-up Silistix has unveiled tools that it claims will free IC designers from slavery to a single system clock by allowing them to stitch together IC-design blocks with the company's asynchronous IP bus. Asynchronous design has thus far been a practical methodology only for advanced designers, but with its IP and EDA combo, Silistix believes it can make the methodology more accessible to mainstream ASIC and SOC (system-on-chip) designers. The company introduced

itself and its Chain-fabric asynchronous-bus IP last December. Now, it is releasing the tools that implement the bus.

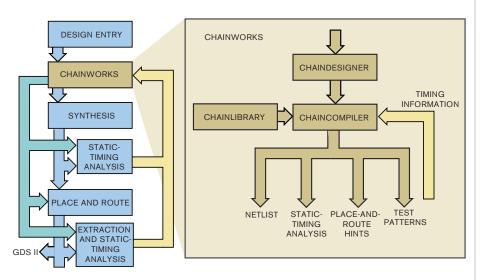

The ChainWorks flow comprises two tools that plug into the traditional ASIC/SOC-design flow and a library. The Chaindesigner graphical-entry tool helps users arrange IP and proprietary-logic blocks in their designs and then interconnect them to come up with a desired network topology. Users feed the tool Verilog, SystemVerilog, or SystemC, allowing them to define initiators and targets, as well as the ports for the initiators and targets, according to David Fritz, the company's vice president of marketing. He claims that users prefer the tool's GUI because it provides a more formal mechanism for visualizing, understanding, and designing the interconnect. A future version of the GUI will allow designers to embed notes in the design to better monitor progress and describe intent.

After users design a topology, the tool generates Verilog and SystemC models and testbenches for simulation, as well as constrained Chain netlists for input to Chaincompiler. After designers have verified their design topology, they can then use the Chaincompiler

Asynchronous design has thus far been a practical methodology only for advanced designers, but with its IP and EDA combo, Silistix believes it can make the methodology more accessible to mainstream ASIC and SOC designers.

asynchronous-synthesis tool to implement the design, interconnecting the various blocks with the company's Chain-fabric bus. Chaincompiler uses the proprietary-asynchronousinterconnect Chainlibrary of components to produce the structural netlist. "Chaincompiler combines the library components to construct your interconnect network and then generate a structural netlist that goes into conventional logic-synthesis tools, such as Synopsys Design Compiler," says Fritz. It also generates static-timing-analysis scripts, place-and-route hints critical for self-timed circuits, and test patterns.

The first release supports scan insertion for interconnect ports, and a future release will include partial-scan BIST (built-in self-test). Users can run iterations between Chain-Works and synthesis, timing analysis, place and route, and extraction. However, most users need to go through the flow only once. The company believes that the flow will open asynchronous design to mainstream use, although it so far has no customer tape-outs to report. It has, however, developed a test chip in-house and claims that unnamed customers are using the tool on current projects.

-by Michael Santarini Silistix, www.silistix.com.

The ChainWorks flow comprises two tools that plug into the traditional ASIC/SOC-design flow and a library.

#### **DILBERT** By Scott Adams

# **EPIC Solutions for Real World Problems**

# Rugged, Reliable, and Ready-to-go

Based on the Embedded Platform for Industrial Computing (EPIC), the EPX-C3 combines the processor and I/O functions required for medical, transportation, instrumentation, communication, MIL/COTS, security, and other demanding applications.

- Fanless 733MHz C3 Processor

- Up to 2GB Flash memory

- 4x AGP CRT/LCD controller

- 10/100 Mbps Ethernet

- USB 2.0 support

- 4 COM channels

- 24 Digital I/O lines

- EIDE, FDC, and Kybd controllers

- PC/104 & PC/104-Plus expansion

- -40°C to +85°C operation

- Size: 4.5" x 6.5" (115mm x 165mm)

- Quick Start Developers kits for Windows® XP, CE, and Linux

Profit from our proven experience. We look forward to the opportunity to demonstrate how our success in the industrial market can work for you.

Call 817-274-7553 or Visit www.winsystems.com Ask about our 30-day product evaluation!

0000000000000

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

### 1U, half-rack switching units' debut kicks off supplier's LXI push

he proponents of LXI (LAN extensions for instrumentation), Ethernet-based interconnect and packaging technology for test-and-measurement products, are confident that LXI overcomes the most serious shortcomings of card-cagebased modular approaches, such as PXI and the older and larger VXI. Moreover, advocates believe that LXI is the first modular-instrument technology that works equally well on the benchtop and in testand-measurement systems. Agilent, one of the companies that led the way in developing LXI, is now among the first to

offer LXI-based products. Agilent based the seven new, 1U (1.75-in.)-high, half-rackwidth L4400-series modules on plug-in cards for the vendor's eight-slot 34980A modular switch/measure mainframe, which is now also LXIcompatible. The new units enable smaller, lower cost configurations for systems that don't need eight plug-in cards and can benefit from locating the signal-switching functions inches away from the unit un-

Each unit surrounds its card with a protective shell that also houses an ac-line-operated power supply. The seven units

The 1U-high, half-rack-width switching and data-acquisition units in the LXI-based L4400 series suit applications that need fewer than eight cards and can benefit from placing the system inputs and outputs close to the unit under test.

are a 40-channel armature-relay multiplexer; a four-byeight-point reed-relay matrix; a 32-channel general-purpose switch: a microwave switch with an external attenuator driver; a 64-bit digital-I/O unit with memory; a four-channel DAC with memory; and a multifunction unit with 32 digital-I/O points, two DACs, and a counter. Prices for these units range from \$1506 to \$2709. The company also offers a \$350, rack-mountable shelf, which can house one or two half-rack-width LXI units, including units that are taller than the 1U-high L4400-series products.

The units' graphical-interface software supports the L4400 series and 34980A. According to the company, this software, which you can operate remotely through a LAN-connected computer with a standard Web browser, goes well beyond the requirements of the LXI standard. The password-protected, operating-system-independent software enables setup, debugging, and troubleshooting of signal-switching systems, including checking configurations; opening, closing, sequencing, and monitoring switches; and sending and capturing SCPIs (standard commands for programmable instruments). The software incorporates an I/O analyzer that lets you examine the error queue and provides status reports that include calibration status and a count of the number of times each relay has operated. You can try out an interactive demo of the software at www.agilent.com/ find/L4400.

-by Dan Strassberg ▶Agilent Technologies, www.agilent.com/find/L4400.

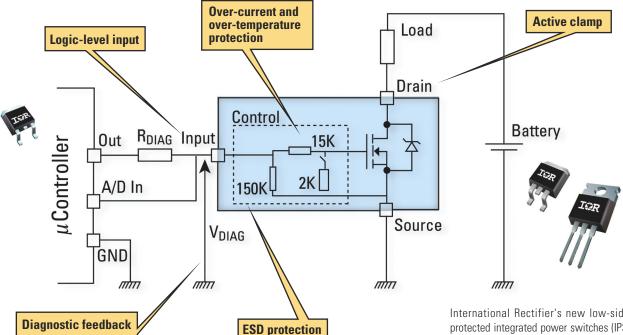

### Chip improves efficiency of flyback-converter circuits

Secondary-side SR (synchronous-rectification) circuits in highpower-flyback- and half-bridge-converter circuits have drawbacks: They can be difficult to design, and they may be subject to patent and licensing restrictions. In addition, their use of a current-transformer circuit to sense polarity changes in the rectifying MOSFETs results in a large, energy-wasting, unused cur-

rent that oscillates between the transformer and the output-filter capacitor.

The IR1167 Smart-Rectifier IC directly and precisely senses the voltage threshold across the SR MOSFET.

Addressing these issues, International Rectifier's new IR1167 SmartRectifier IC directly and precisely senses the voltage threshold across the SR MOSFET. The company claims that the chip can increase system efficiency by 1% by halving the losses the MOSFET dissipates and reducing the MOSFET's temperature by 10°, thus reducing

the number of MOSFETs or allowing a change in part size from TO-220 to SO-8 packages. The device is also available in DIP-8 packages.

The SmartRectifier works with the IRF7853, the IRFB4110, and the IRFB4227 MOSFETs, which feature low on-resistance and gate-charge characteristics. The device sells for \$1.08 (10,000).-by Margery Conner

▶International Rectifier, www.irf.com.

#### FROM THE VAULT

By 2006, then, the television, which we think of today as our window on the world, will fill a

much, much larger position in our lives. Of course, the TV itself will evolve dramatically from a mere display device, becoming an intelligent two-way medium that combines telephone, television, and computer, It will control appliances (even robots) in the home; do our bookkeeping; compute our taxes; buy and sell stocks; make airline, hotel, and theater reservations; teach and entertain us; enable us to work at home; and even give us advice. And it will provide all of these functions at a reasonable price.

Thomas J Lonergan, president and co-founder, Wolfdata Inc, EDN, Oct 14, 1981.

**Design Reuse**

**Board Integration** HW/SW Partitioning

Booth 13306

# Think Embedded? Peripherals

**Need to Customize Verification**

**Spend Less**

Programmable Hardware

CPU Cores Think FPGAs.

Risk Reduction Obsolescence-Proof

Development Tools Do More

Hardware Acceleration Nins I

High Performance Think Altera. Low Cost

Custom Instructions Multi-Core Design

Get There First

When it's time to design your next embedded system, think Altera. Use our FPGAs for coprocessing or peripheral expansion for your CPU. Or use our Nios<sup>®</sup> II soft-core processor to quickly create your own stand-alone custom microcontroller. Either way, Altera offers the flexibility to improve your team's productivity and time-to-market while lowering system cost and reducing the risk of obsolescence.

If you're thinking of your next embedded design, think FPGAs—think Altera.

- World's top 20 electronic OEMs are already using Altera embedded solutions

- Over 15,000 Nios II licenses worldwide

- Support for industry-standard tools and operating systems

The Programmable Solutions Company®

www.altera.com

# **VOICES**

### **Economies of Freescale**

ichel Mayer, chairman and chief executive officer of Freescale Semiconductor, discusses his company's future, the shift to low-power processors, and the source of future competition. An excerpt of that interview follows. You can find the complete interview at www.reed-electronics.com/ electronicnews/article/CA6308384.

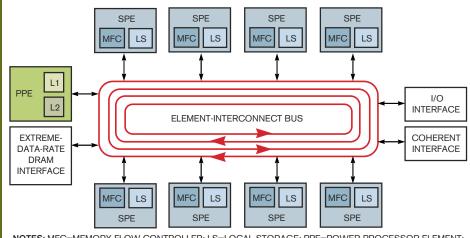

#### Do you see a shift in the processor market toward multiple processors rather than a single extremely powerful processor?

Yes. I am completely convinced of that [scenariol. The center of innovation is moving away from the PC and IT. There will always be a market for faster, CMOS-core processors. But, frankly, the bulk of the market is going to distributed processing and low power. Intel [www.intel.com] essentially accepted premise and said that multicore is the way to go. But, even beyond that, there will be a whole set of more efficient, low-power processors.

#### Will they be general processors or custom processors?

The architectures will be general, whether it's ARM [www.arm.com] PowerPC or some simpler types. I believe the change will be in the applications. More types of SOCs [systems on chips] will include these processors.

#### Who becomes your chief competition in this market, assuming that it's neither AMD [www.amd.com] nor Intel?

Over time, Intel and AMD will have to branch out. In the cell-phone and the portable areas, it is still TI [www.ti.com], Philips [www. Philips.com, and STMicrolectronics [www.st.com]. A few companies have multimedia consumer applications. And, of course, in DSPs, TI has some. In the automotive industry, that's more Microchip, NEC, Renesas, and Infineon with its TriCore [www.microchip.com, www.necel.com, www.renesas. com, www.infineon.com]. More and more companies are using ARM, which is more of a general processor that finds use across segments. We believe our PowerPC will play an important role in embedded processors.

#### Will it be a volume game, in which you produce in huge quantities, or will it be about specialization?

Some applications are high-volume by themselves. Whether or not you have a completely custom solution, they are already in high volume. A case in point is gaming. The gaming processors, whether Playstations or Xbox 360s, are fully customized. If they're completely customized and not high-volume, you have to be generic. By the way, even Intel wasn't completely successful in the general-processor space. It was highly successful in one application: the PC. It's difficult to take a PC processor and branch out. There's not a lot of customization you can do. So, to answer

your question, things will need to remain customized. What's happening as we evolve is that with SOC techniques and mixand-match IC libraries, it makes it possible for those segments to share more.

#### What effect does a combination of commonality and customization have on your costs at advanced architectures?

It's not only a problem with processors. It's a problem with the whole SOC.

#### Typically, the only way to offset that problem has been with high volume.

There are several ways to achieve high volume to offset your R&D. One is to have better IP [intellectualproperty] reuse-better commonality. That's the wave of the future. A lot of key players are developing design strategies that allow you to more easily reuse such things as communication blocks, because everyone now needs to access the Internet. The design techniques will evolve to be more flexible. Otherwise, you cannot solve your R&D dilemma.

#### What effect has the Crolles Alliance with Philips and STMicro had on vour R&D costs?

Anything that helps develop some of the common processes is good. Partnerships are now becoming increasingly important in this industry. Crolles is one of the most publicized, but we have a lot of other partnerships in IP and joint developments with our customers and partners. We've been focusing a lot on process development and manufacturing and the need to have critical mass to remain as an IDM [integrateddevice manufacturer]. The need to have a broad portfolio of IP to be able to offer multifunction SOCs and mix of analog and digital functions will be drivers for consolidation. It's not just at the IDM level. A lot of companies are going to have to either be good at partnering or be integrated.

#### Do you see any shift in where your products are ending up?

Assembly and test are happening in Asia, but there are still wafer fabs in the United States and, to a lesser extent, in Europe. The foundry work is occurring in Asia. AMD is investing in Dresden, Germany. Intel is in the United

#### You've now been at Freescale since mid-2004. which is enough time to really understand the company. What's your biggest challenge?

Getting enough talent. We're making great progress along those lines, but it continues to be a challenge. Also, changing the culture of the company. We have a lot of challenges: the market, the technology, the manufacturing. If I can bring in the same kind of talent that I've brought in so far, if we can change the culture, we can do great things.

> -by Ed Sperling, Editor in Chief, Electronic News

# Blackfin is action packed

#### **Streaming Media**

High Definition

Effects Processing

Triple Play

Image Processing

VoIP

**Embedded Security**

GSM/EDGE

Baseband Processing

Digital Radio

**Global Positioning**

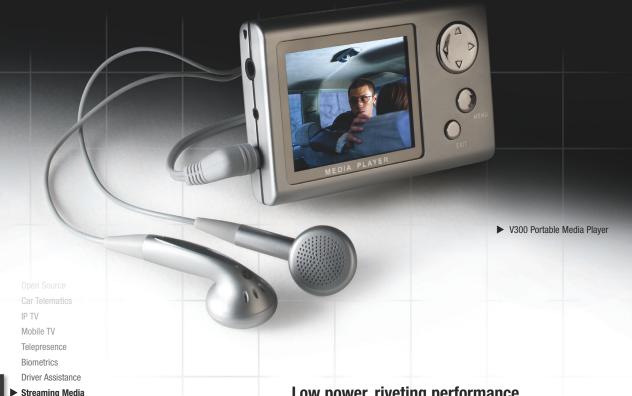

#### Low power, riveting performance

The V300 Portable Media Player needed a processor that could enable 8 hours of MPEG-4 or MJPEG video playback and 16 hours of MP3 music, and run its operating system and application set. After auditioning a long list of prospects, Blackfin® got the role. Why? Blackfin easily met the V300's performance goals while powering the system from a 600 mAh battery. Then Blackfin nailed the part with \$5 to 1200 GMACS scalable performance for content and applications.

Get started using Blackfin now: analog.com/blackfin-is-everywhere

© 2005 Analog Devices, Inc.

#### **MRESEARCH UPDATE** BY MATTHEW MILLER

### Plastic substrate allows OLED displays to get bent

esearchers at GE Plastics have detailed a plastic-substrate system that they claim will lead to OLED (organic-light-emittingdiode)-based displays that are more flexible, lighter, more durable, and less costly to build than those based on glass substrates.

The system combines a high-temperature Lexan polycarbonate film with a transparent coating that protects the display from oxygen and moisture. The high clarity and high temperature resistance of the Lexan film enable the construction of a 125-micronthick substrate that can withstand the heat involved in OLED fabrication and still allow optimal light transmission, according to the company. In addition, the system should be amenable to high-volumemanufacturing processes that will drive down cost.

**⊳GE Plastics**, www. geplastics.com.

#### Nanotube-based ultracapacitors could rival batteries

Researchers at the Massachusetts Institute of Technology (Cambridge, MA) report that an electrode structure based on a matrix of vertically aligned carbon nanotubes could drastically improve the energy density of ultracapacitors. Whereas the energy density of commercial ultracapacitors tops out at 6 Whr/kg, a nanotube-based version could offer 60 Whr/kg-comparable to lithium-ion batteries, the researchers claim. Meanwhile, such a device could provide power density of 100 kW/kg-three orders of magnitude better than lithium-ion batteries-and 300,000-cycle durability. For more information, go to http://web.mit.edu/ newsoffice/2006/batteries-0208.html.

Massachusetts Institute of Technology,

### Standard silicon conjures continuous laser

ntel researchers claim to have attained a significant industry first: a continuouswave laser that the company built using a standard siliconmanufacturing process. The advance could lead to a new generation of low-cost lasers that designers could integrate with standard electronics for applications in highspeed interconnect and medical devices.

The 15×15-mm chip routes light from an external source through an S-shaped waveguide that's etched into the silicon and coated with a reflective thin-film material. Natural atomic vibrations in the silicon amplify the light in the well-known Raman-effect phenomenon, which is 10,000 times stronger in silicon than it is in glass fibers.

In addition, the researchers employ a PIN-semiconductor structure to mitigate the twophoton-absorption effect, in which two photons from the light source collide with an atom within the waveguide, knocking free an electron. The PIN structure acts as a "vacuum" that prevents these excess electrons from accumulating and absorbing so much light that the laser stops functioning, according to the company.

Visit the Web version of this article at www.edn.com/ 060330ru1 for a link to additional background, including video, animation, and coverage from the journal Nature. ▶Intel Corp, www.intel. com.

Intel claims that this laser-generating chip, built using a standard silicon process, could drive low-cost, diminutive lasers into applications including high-speed, on-chip interconnect.

# Blackfin is picture perfect

VoIP Embedded Security GSM/EDGE Baseband Processing Digital Radio Global Positioning

Packet Processing GCC/Linux Cryptography

Rights Management

Car Telematics

Mobile TV

To equip professionals with a powerful and compact photography module for its analog SLR cameras, Leica Camera AG needed a small high performance processor. So the company focused on Blackfin's advantages. These included dual-processing cores up to 600 MHz that use just 144 mm² of board space, and Blackfin's ability to do Leica's color interpolation, auto exposure, auto white balance, gamma correction, and JPEG compression of 10 megapixel images. Smaller footprint, higher performance: No wonder Blackfin® is everywhere.

Get started using Blackfin now: analog.com/blackfin-is-everywhere

#### AGLOBAL DESIGNER

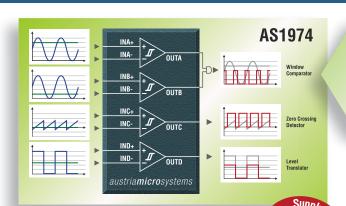

### DAQ chips simplify sensor interfaces

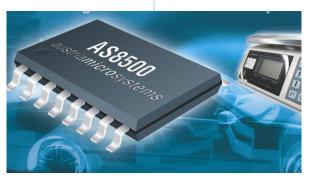

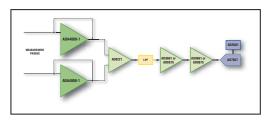

ou can connect a wide variety of sensors to digital systems using austriamicrosystems' AS8500 and AS8501 chips to perform the analog-front-end and analog-to-digital-conversion function. The devices comprise a chopper input, a programmable-gain preamplifier, a 16-bit ADC, and a DSP filter block. They allow you to make direct connection to very-low-level sensor signals, such as lowvalue current-sense resistors or thermocouples, and operate from a single 5V supply. The chips offer resolution of less than 1  $\mu V$  and linearity error below 0.1%, with sampling rates as high as 16 kHz. Applying correction in the digital section of the chip provides offset-free operation, and external averaging allows systems to achieve resolution of 21 bits. The chopper-input stage handles a maximum of four inputs, which you can use as single-ended, ground-referring connections or in pairs in a fully differential mode.

The company delivers the 8500 with a standard trim setting; for higher precision, the 8501 provides a calibration routine that characterizes each chip's functional analog parameters at final test and writes a set of trimming values into internal registers on the silicon. Internal-register settings also control the chips' configuration, and you can rewrite them at any time. The delivered default configuration is a read-only converter. Likewise, you set register values to select programmable gain of 6, 24, 50, or 100 to select fullscale measurement ranges of 7 to 120 mV. A three-wire serial interface outputs filtered digital data to a host system.

With austriamicrosystems' focus on mixed-signal design, the chip's designers gave particular attention to internal decoupling between analog and digital circuitry, part of a strategy to achieve low noise. Offset is less than 500 nV, and temperature-coefficient offset is negligible.

The chip also integrates a precision voltage reference, a temperature-measurement element, and a digital comparator. The parts operate over  $-40 \text{ to } +125^{\circ}\text{C}$  and suit use in automotive and industrial applications. To monitor current in a vehicle-battery lead, a 100-μ $\Omega$  sense resistor provides measurement resolution of 10 mA in a full-scale range of 1500A. Self- and systemcalibration routines run at power-up. The AS8500/1 chips sell for €5.50 (\$6.60) and €6.60 (\$7.90), respectively (1000).

-by Graham Prophet, EDN Europe

www.austriamicrosystems.

With the AS8500/1 chips, you can build a complete low-noise, precision sensor-signal-conditioning front end to a microcontroller-based system.

### Headphone amp swaps modes to cut noise, save power

Designers working with portable audio products have a new option in the constant tradeoff of performance versus battery life: Wolfson's WM8985 audio codec. The device has a headphone-output stage that is dynamically switchable from operation in Class A/B to operation in Class D. Class A/B offers a conventional route to a high-quality, low-distortion output but requires a standing current through its output-stage devices and has a higher power demand. Class D has lower losses. A spokesman for Wolfson makes the subtle point that, in Class D, headphone driving is about power consumption rather than power dissi

Although manufacturers in recent years have greatly refined the quality of Class D amplifiers, designers may sometimes not want to use them. Class D is by definition a switching-output mode and introduces some level of harmonics and noise. In a device such as a smart phone with an MP3 player, designers may want it to operate in Class D when the RF section of the handset is not active and in Class A/B when it is. In handsets with FM radio, Wolfson notes, the headphone lead is also typically the FM antenna and cannot carry Class D-output waveforms while receiving FM.

Switching on the fly between modes, the codec can accommodate this requirement. At typical power outputs of 10 mW, switching to Class D reduces power consumption by approximately 50%. The 8985 also integrates a DSP for filtering and equalization, differential or line inputs, audio mixing, and a PLL that can accept a wide range of clock inputs. It has a switchable output and one that is in permanent Class A/B mode. SNR figures for the device's DAC, ADC, and headphone driver are 98, 92.5, and 90 dB, respectively. In standby mode, the device uses 360 µW.-by Graham Prophet, EDN Europe

Wolfson Microelectronics, www.wolfsonmicro.com.

# UNLEASH BROADBAND WITH FUJITSU'S WIMAX 802.16-2004 SoC.

With a MAC-to-PHY implementation based on the IEEE 802.16-2004 broadband wireless access standard, the Fujitsu WiMAX SoC, MB87M3400, offers a cost-effective solution for both subscriber station and base station applications. This highly integrated SoC implements MAC, PHY, radio control and all the necessary analog circuits for the appropriate 2 to 11GHz licensed or license-exempt bands. The Fujitsu WiMAX SoC fully complies with the IEEE 802.16-2004 standard using an OFDM PHY.

#### **ADVANCED FEATURES**

- 256 OFDM PHY with 64QAM, 16QAM, QPSK and BPSK modulation

- Uplink subchannelization

- Flexible baseband interface with integrated high-performance ADC and DAC

- Security implementation using DES, CCM encryption/decryption

- Rich set of integrated peripheral and RF control

For more information, call (800) 866-8608 or visit http://us.fujitsu.com/micro/wimax

# RAMAC launched disk-drive revolution

developed the Mark 1 calculating machine in the 1930s, and researchers at the University of Pennsylvania completed the ENIAC (electronic numerical integrator and computer) in 1945. Many technology historians consider ENIAC the first successful general-purpose digital computer. But the 305 RAMAC (random-access-method-of-accounting-and-control) system, which debuted in September 1956, was the first to include near-line random-access storage in the form of the IBM 350 Disk File. Before the emergence of the Disk File, core, tape, and drum

omputers weren't new back in the fall of 1956. IBM

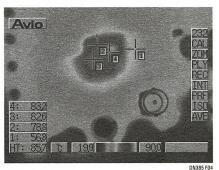

The Disk File afforded access to effectively 4.4 Mbytes of data, for the first time making the real-time retrieval and manipulation of database records a reality. The Disk File featured 50 24-in. disks that stored 5 million 7-bit characters. At the product's launch, IBM claimed that, to realize similar capacity using drum memory, one would have had to use a 42-ft-long, 13-in.-diameter

memory provided the only storage option.

drum. IBM leased the 305 RAMAC with the 350 Disk File for \$35,000 per

Although the size of the 350 Disk File—60×68×29 in.—bears little resemblance to modern disk drives, its electromechanical design is remarkably similar to that of today's drives. It used a stack of iron-oxide-coated aluminum platters with magnetic-recording surfaces on each side. But it used only a single pair of heads that a motor had to move to predetermined positions on a vertical "way" to the disk of interest. Once the heads reached the correct position, a pneumatic cylinder moved the heads laterally to a position straddling the platter of interest. Amazingly, the design achieved a maximum seek time of 0.7 sec, and an NRZ (nonreturn-to-zero) recording scheme yielded a transfer rate close to 9 kbytes/sec.

Perhaps the best technical account of RAMAC and the Disk File is from the MHDC (Magnetic Disk Heritage Center, www.sjmdhc.org). The MHDC hosts an exhibit in the building that housed the original IBM lab. The MDHC pegs several other milestones that came on the heels of RAMAC that refined the electromechanical design in today's disk drives. Even before IBM delivered RAMAC, the lab was working on the prototype of the ADF (Advanced Disk File), which would appear in 1961 in the 50-Mbyte IBM 1301. The ADF achieved what IBM called "real-time, online, direct-access storage" by dedicating a flying head to each surface. In contrast, IBM pitched the RAMAC Disk File as "online, direct-access storage." The ADF also pioneered perpendicular recording, although both RAMAC and products that appeared after the 1301 used longitudinal recording.

Later, IBM added servo-control information stored on the disks in the SDF (Single-Disk File); both RAMAC and ADF used open-loop control systems. SDF technology came to market as the IBM 3330 in 1971. The 3330 featured a 2-Mbyte removable disk pack, although the fixed-platter design returned later and remains the high-volume architecture. And the capacity march has never slowed. Today, for instance, Hitachi ships 1-in. Microdrives that store 8 Gbytes. Some projections have small MP3 players storing 3 Tbytes or more by 2020.EDN

# Random Memory

NEW YORK, N.Y.—Built around the IBM disc memory, a random access memory unit has a storage capacity of 5,000,000 digits. Any of these digits can be reached directly without scanning through intervening records. The memory unit consists of 50 magnetic metal discs arranged in a vertical stack. Both sides of the discs are used for recording data, so 100 disc faces are available for storage. There are 100 recording tracks on

The 50-platter IBM 350 Disk File featured a single pair of heads that moved vertically to reach the platter of interest and yielded a maximum seek time of 0.7 sec (courtesy Magnetic Disk Heritage Center).

each disc face, and each track will hold a stack of ten 100-character records. The entire stack rotates at 1200 rpm, so that any address in the memory can be located in milliseconds.

Designed and produced by IBM, the Model 305 RAMAC uses punched card input and punched card and printer output. This data processing machine relies upon a powerful combination of stored program and control panel wiring for instructions. EDN, November 1956

# The Digi-Key Difference

# Digi-Key is the Leader Among Distributors on the Web

Digi-Key consistently leads the pack among distributors in virtually all areas of web site proficiency and performance.

All rankings based on EE Times Distributor Evaluation Study, September 2005, conducted by Beacon Technology Partners, LLC

1.800.344.4539 - www.digikey.com

# SIGNAL INTEGRITY

# BY HOWARD JOHNSON, PhD

# Terminator II

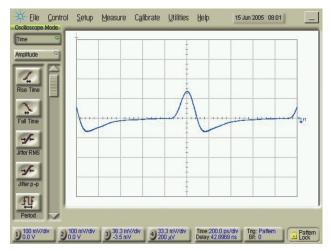

n my last column, I presented a rather troubled system architecture with incredibly stringent signal-quality requirements (Reference 1). The signal source is a low-impedance ECL driver with a 400psec rise time, which connects to the receiver by 3 ft of RG58 A/U

Somebody else already built the signal source, so you are stuck with the low-impedance ECL output. By government contract, you must design the receiver using an off-the-shelf FPGA combined with an external  $50\Omega \pm 1\%$  terminating resistor.